Created

January 20, 2023 15:09

-

-

Save cyring/d0ff0cdd89fc37b0ec2ed6037e218b79 to your computer and use it in GitHub Desktop.

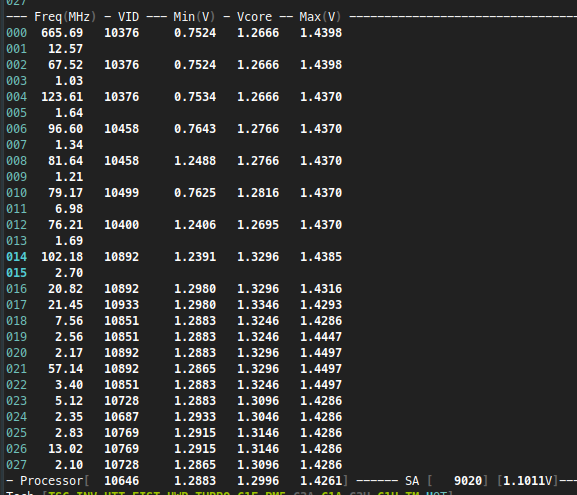

i9-13900K

This file contains bidirectional Unicode text that may be interpreted or compiled differently than what appears below. To review, open the file in an editor that reveals hidden Unicode characters.

Learn more about bidirectional Unicode characters

| 13th Gen Intel(R) Core(TM) i9-13900K |

Author

cyring

commented

Jan 20, 2023

•

Sign up for free

to join this conversation on GitHub.

Already have an account?

Sign in to comment