Last active

December 28, 2022 10:17

-

-

Save cyring/32df20caa4034cb74500d16507a9bbe1 to your computer and use it in GitHub Desktop.

EPYC 7713

This file contains bidirectional Unicode text that may be interpreted or compiled differently than what appears below. To review, open the file in an editor that reveals hidden Unicode characters.

Learn more about bidirectional Unicode characters

| AMD EPYC 7713 64-Core Processor |

Author

cyring

commented

Dec 28, 2022

Zen UMC [1650]

Controller #0 Eight Channel

Bus Rate 1600 MHz Bus Speed 1599 MHz REG DDR4 Speed 3199 MT/s

Cha CL RCDr RCDw RP RAS RC RRDs RRDl FAW WTRs WTRl WR clRR clWW

#0 24 22 22 22 52 74 4 8 16 4 12 24 5 5

#1 24 22 22 22 52 74 4 8 16 4 12 24 5 5

#2 24 22 22 22 52 74 4 8 16 4 12 24 5 5

#3 24 22 22 22 52 74 4 8 16 4 12 24 5 5

#4 24 22 22 22 52 74 4 8 16 4 12 24 5 5

#5 24 22 22 22 52 74 4 8 16 4 12 24 5 5

#6 24 22 22 22 52 74 4 8 16 4 12 24 5 5

#7 24 22 22 22 52 74 4 8 16 4 12 24 5 5

CWL RTP RdWr WrRd scWW sdWW ddWW scRR sdRR ddRR drRR drWW drWR drRRD

#0 20 12 11 3 1 6 6 1 4 4 0 0 0 0

#1 20 12 12 3 1 6 6 1 4 4 0 0 0 0

#2 20 12 12 3 1 6 6 1 4 4 0 0 0 0

#3 20 12 12 3 1 6 6 1 4 4 0 0 0 0

#4 20 12 12 3 1 6 6 1 4 4 0 0 0 0

#5 20 12 12 3 1 6 6 1 4 4 0 0 0 0

#6 20 12 12 3 1 6 6 1 4 4 0 0 0 0

#7 20 12 12 3 1 6 6 1 4 4 0 0 0 0

REFI RFC1 RFC2 RFC4 RCPB RPPB BGS:Alt Ban Page CKE CMD GDM ECC

#0 12480 560 416 256 0 0 OFF ON R1W1 0 8 1T OFF 1

#1 12480 560 416 256 0 0 OFF ON R1W1 0 8 1T OFF 1

#2 12480 560 416 256 0 0 OFF ON R1W1 0 8 1T OFF 1

#3 12480 560 416 256 0 0 OFF ON R1W1 0 8 1T OFF 1

#4 12480 560 416 256 0 0 OFF ON R1W1 0 8 1T OFF 1

#5 12480 560 416 256 0 0 OFF ON R1W1 0 8 1T OFF 1

#6 12480 560 416 256 0 0 OFF ON R1W1 0 8 1T OFF 1

#7 12480 560 416 256 0 0 OFF ON R1W1 0 8 1T OFF 1

MRD:PDA MOD:PDA WRMPR STAG PDM RDDATA WRD WRL RDL XS XP CPDED

#0 32 16 25 25 0 187 0:F:1 19 2 15 26 576 10 4

#1 32 16 25 25 0 187 0:F:1 19 2 15 26 576 10 4

#2 32 16 25 25 0 187 0:F:1 19 2 15 26 576 10 4

#3 32 16 25 25 0 187 0:F:1 19 2 15 26 576 10 4

#4 32 16 25 25 0 187 0:F:1 19 2 15 26 576 10 4

#5 32 16 25 25 0 187 0:F:1 19 2 15 26 576 10 4

#6 32 16 25 25 0 187 0:F:1 19 2 15 26 576 10 4

#7 32 16 25 25 0 187 0:F:1 19 2 15 26 576 10 4

DIMM Geometry for channel #0

Slot Bank Rank Rows Columns Memory Size (MB)

#0 16 1 131072 1024 16384 M393A2K40DB3-CWE

#1

DIMM Geometry for channel #1

Slot Bank Rank Rows Columns Memory Size (MB)

#0 16 1 131072 1024 16384 M393A2K40DB3-CWE

#1

DIMM Geometry for channel #2

Slot Bank Rank Rows Columns Memory Size (MB)

#0 16 1 131072 1024 16384 M393A2K40DB3-CWE

#1

DIMM Geometry for channel #3

Slot Bank Rank Rows Columns Memory Size (MB)

#0 16 1 131072 1024 16384 M393A2K40DB3-CWE

#1

DIMM Geometry for channel #4

Slot Bank Rank Rows Columns Memory Size (MB)

#0 16 1 131072 1024 16384 M393A2K40DB3-CWE

#1

DIMM Geometry for channel #5

Slot Bank Rank Rows Columns Memory Size (MB)

#0 16 1 131072 1024 16384 M393A2K40DB3-CWE

#1

DIMM Geometry for channel #6

Slot Bank Rank Rows Columns Memory Size (MB)

#0 16 1 131072 1024 16384 M393A2K40DB3-CWE

#1

DIMM Geometry for channel #7

Slot Bank Rank Rows Columns Memory Size (MB)

#0 16 1 131072 1024 16384 M393A2K40DB3-CWE

#1

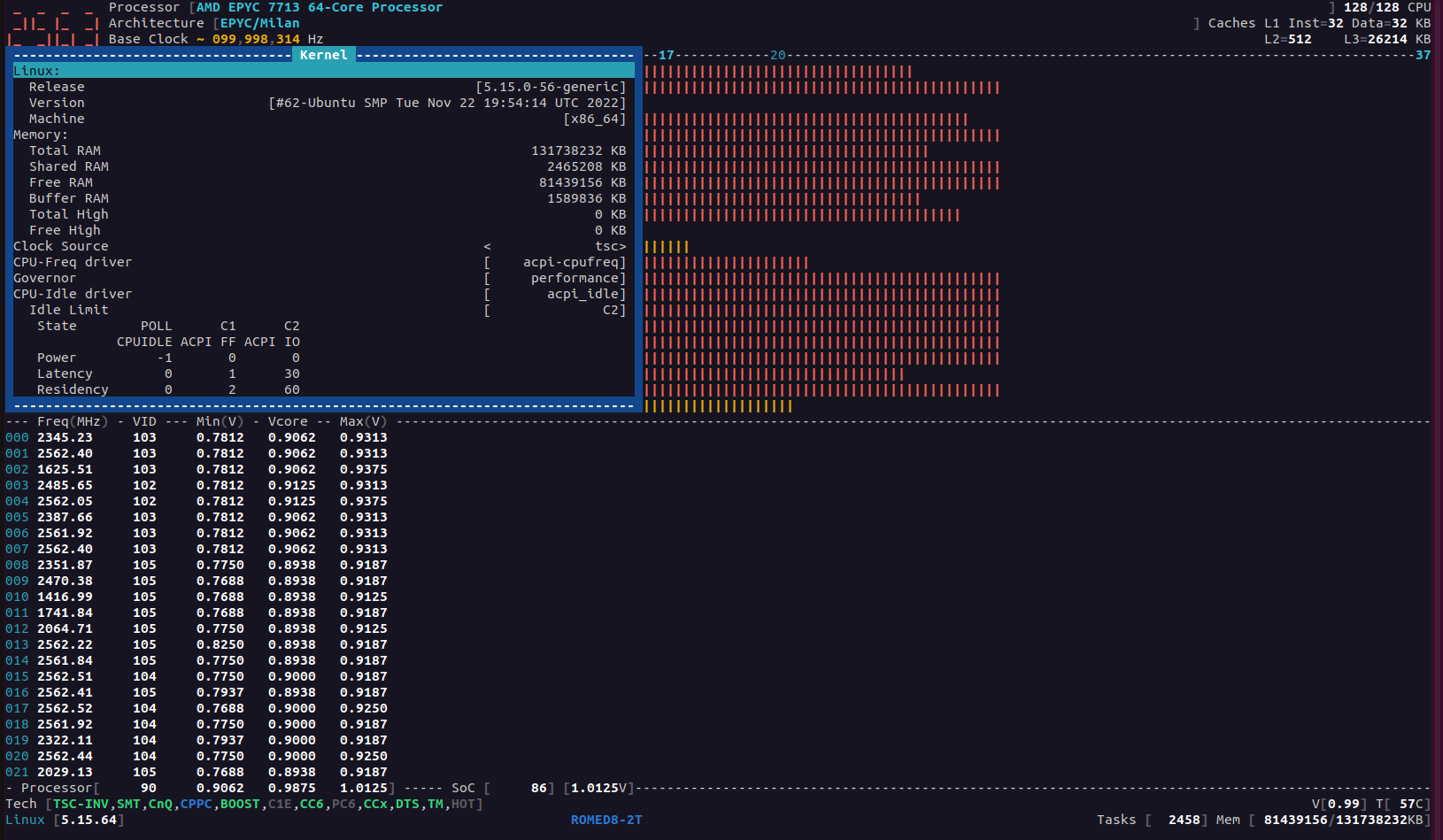

Processor [AMD EPYC 7713 64-Core Processor]

|- PPIN# [ 2b5f958e276c00f]

|- Architecture [EPYC/Milan]

|- Vendor ID [AuthenticAMD]

|- Microcode [0x0a001173]

|- Signature [ AF_01]

|- Stepping [ 1]

|- Online CPU [128/128]

|- Base Clock [ 99.988]

|- Frequency (MHz) Ratio

Min 1499.82 < 15 >

Max 1999.76 < 20 >

|- Factory [100.000]

2000 [ 20 ]

|- Performance

|- P-State

TGT 1999.76 < 20 >

|- CPPC

Min 399.95 < 4 >

Max 3699.55 < 37 >

TGT 3699.55 < 37 >

|- Turbo Boost [ LOCK]

XFR 3699.55 [ 37 ]

CPB 3699.55 [ 37 ]

1C 1699.79 < 17 >

2C 1499.82 < 15 >

|- Uncore [ LOCK]

CLK 1599.81 [ 16 ]

MEM 4799.42 [ 48 ]

Instruction Set Extensions

|- 3DNow!/Ext [N/N] ADX [Y] AES [Y] AVX/AVX2 [Y/Y]

|- AVX512-F [N] AVX512-DQ [N] AVX512-IFMA [N] AVX512-PF [N]

|- AVX512-ER [N] AVX512-CD [N] AVX512-BW [N] AVX512-VL [N]

|- AVX512-VBMI [N] AVX512-VBMI2 [N] AVX512-VNNI [N] AVX512-ALG [N]

|- AVX512-VPOP [N] AVX512-VNNIW [N] AVX512-FMAPS [N] AVX512-VP2I [N]

|- AVX512-BF16 [N] AVX-VNNI-VEX [N] AVX-FP128 [N] AVX-FP256 [Y]

|- BMI1/BMI2 [Y/Y] CLWB [Y] CLFLUSH [Y] CLFLUSH-OPT [Y]

|- CLAC-STAC [Y] CMOV [Y] CMPXCHG8B [Y] CMPXCHG16B [Y]

|- F16C [Y] FPU [Y] FXSR [Y] LAHF-SAHF [Y]

|- MMX/Ext [Y/Y] MON/MWAITX [Y/Y] MOVBE [Y] PCLMULQDQ [Y]

|- POPCNT [Y] RDRAND [Y] RDSEED [Y] RDTSCP [Y]

|- SEP [Y] SHA [Y] SSE [Y] SSE2 [Y]

|- SSE3 [Y] SSSE3 [Y] SSE4.1/4A [Y/Y] SSE4.2 [Y]

|- SERIALIZE [N] SYSCALL [Y] RDPID [Y] UMIP [Y]

|- VAES [Y] VPCLMULQDQ [Y] PREFETCH/W [Y] LZCNT [Y]

Features

|- 1 GB Pages Support 1GB-PAGES [Capable]

|- 100 MHz multiplier Control 100MHzSteps [Missing]

|- Advanced Configuration & Power Interface ACPI [Capable]

|- Advanced Programmable Interrupt Controller APIC [Capable]

|- Advanced Virtual Interrupt Controller AVIC [Missing]

|- APIC Timer Invariance ARAT [Capable]

|- Clear Zero Instruction CLZERO [Capable]

|- Core Multi-Processing CMP Legacy [Capable]

|- L1 Data Cache Context ID CNXT-ID [Missing]

|- Collaborative Processor Performance Control CPPC [Capable]

|- Direct Cache Access DCA [Missing]

|- Debugging Extension DE [Capable]

|- Debug Store & Precise Event Based Sampling DS, PEBS [Missing]

|- CPL Qualified Debug Store DS-CPL [Missing]

|- 64-Bit Debug Store DTES64 [Missing]

|- Fast Short REP MOVSB FSRM [Missing]

|- Fast-String Operation ERMS [Missing]

|- Fused Multiply Add FMA | FMA4 [Capable]

|- Hardware Lock Elision HLE [Missing]

|- Hardware P-state control HwP [Capable]

|- Instruction Based Sampling IBS [Capable]

|- Instruction INVLPGB INVLPGB [Capable]

|- Instruction INVPCID INVPCID [Capable]

|- Long Mode 64 bits IA64 | LM [Capable]

|- LightWeight Profiling LWP [Missing]

|- Memory Bandwidth Enforcement MBE [Capable]

|- Machine-Check Architecture MCA [Capable]

|- Instruction MCOMMIT MCOMMIT [Capable]

|- Memory Protection Extensions MPX [Missing]

|- Model Specific Registers MSR [Capable]

|- Memory Type Range Registers MTRR [Capable]

|- No-Execute Page Protection NX [Capable]

|- OS-Enabled Ext. State Management OSXSAVE [Capable]

|- Physical Address Extension PAE [Capable]

|- Page Attribute Table PAT [Capable]

|- Pending Break Enable PBE [Missing]

|- Process Context Identifiers PCID [Capable]

|- Perfmon and Debug Capability PDCM [Missing]

|- Page Global Enable PGE [Capable]

|- Page Size Extension PSE [Capable]

|- 36-bit Page Size Extension PSE36 [Capable]

|- Processor Serial Number PSN [Missing]

|- Resource Director Technology/PQE RDT-A [Capable]

|- Resource Director Technology/PQM RDT-M [Capable]

|- Read Processor Register at User level RDPRU [Capable]

|- Restricted Transactional Memory RTM [Missing]

|- Safer Mode Extensions SMX [Missing]

|- Self-Snoop SS [Missing]

|- Supervisor-Mode Access Prevention SMAP [Capable]

|- Supervisor-Mode Execution Prevention SMEP [Capable]

|- Time Stamp Counter TSC [Invariant]

|- Time Stamp Counter Deadline TSC-DEADLINE [Missing]

|- TSX Force Abort MSR Register TSX-ABORT [Missing]

|- TSX Suspend Load Address Tracking TSX-LDTRK [Missing]

|- User-Mode Instruction Prevention UMIP [Capable]

|- Virtual Mode Extension VME [Capable]

|- Virtual Machine Extensions VMX [Missing]

|- Write Back & Do Not Invalidate Cache WBNOINVD [Capable]

|- Extended xAPIC Support x2APIC [ xAPIC]

|- AVIC controller for x2APIC x2AVIC [Missing]

|- XSAVE/XSTOR States XSAVE [Capable]

|- xTPR Update Control xTPR [Missing]

Mitigation mechanisms

|- Indirect Branch Restricted Speculation IBRS [Capable]

|- IBRS Always-On preferred by processor [ Unable]

|- IBRS preferred over software solution [Capable]

|- IBRS provides same speculation limits [Capable]

|- Indirect Branch Prediction Barrier IBPB [Capable]

|- Single Thread Indirect Branch Predictor STIBP [ Enable]

|- Speculative Store Bypass Disable SSBD [Capable]

|- SSBD use VIRT_SPEC_CTRL register [ Unable]

|- SSBD not needed on this processor [ Unable]

|- No Branch Type Confusion BTC_NO [ Unable]

|- BTC on Non-Branch instruction BTC-NOBR [Capable]

|- Arch - No Fast Predictive Store Forwarding PSFD [Capable]

Security Features

|- Secure Init and Jump with Attestation SKINIT [Capable]

|- Secure Encrypted Virtualization SEV [Capable]

|- SEV - Encrypted State SEV-ES [Capable]

|- SEV - Secure Nested Paging SEV-SNP [Capable]

|- Guest Mode Execute Trap GMET [Capable]

|- Supervisor Shadow Stack SSS [Capable]

|- VM Permission Levels VMPL [Capable]

|- VMPL Supervisor Shadow Stack VMPL-SSS [Missing]

|- Secure Multi-Key Memory Encryption SME-MK [Missing]

Technologies

|- Instruction Cache Unit

|- L1 IP Prefetcher L1 HW IP < ON>

|- Data Cache Unit

|- L1 Prefetcher L1 HW < ON>

|- L2 Prefetcher L2 HW < ON>

|- System Management Mode SMM-Lock [ ON]

|- Simultaneous Multithreading SMT [ ON]

|- PowerNow! CnQ [ ON]

|- Core C-States CCx [ ON]

|- Core Performance Boost CPB < ON>

|- Watchdog Timer WDT < ON>

|- Virtualization SVM [ ON]

|- I/O MMU AMD-V [OFF]

|- Version [ N/A]

|- Hypervisor [OFF]

|- Vendor ID [ N/A]

Performance Monitoring

|- Version PM [ 1]

|- Counters: General Fixed

| { 6, 6, 4 } x 48 bits 3 x 64 bits

|- Enhanced Halt State C1E <OFF>

|- C2 UnDemotion C2U < ON>

|- C3 UnDemotion C3U < ON>

|- Core C6 State CC6 < ON>

|- Package C6 State PC6 <OFF>

|- Legacy Frequency ID control FID [OFF]

|- Legacy Voltage ID control VID [OFF]

|- P-State Hardware Coordination Feedback MPERF/APERF [ ON]

|- Core C-States

|- C-States Base Address BAR [ 0x813 ]

|- ACPI Processor C-States _CST [ 2]

|- MONITOR/MWAIT

|- State index: #0 #1 #2 #3 #4 #5 #6 #7

|- Sub C-State: 1 1 0 0 0 0 0 0

|- Core Cycles [Capable]

|- Instructions Retired [Capable]

|- Reference Cycles [Capable]

|- Last Level Cache References [Capable]

|- Global Time Stamp Counter [Missing]

|- Data Fabric Performance Counter [Capable]

|- Core Performance Counter [Capable]

|- Processor Performance Control _PCT [ Enable]

|- Performance Supported States _PSS [ 3]

|- Performance Present Capabilities _PPC [ 0]

|- Continuous Performance Control _CPC [ Enable]

|- Collaborative Processor Performance Control CPPC <FMW>

|- Capabilities Lowest Efficient Guaranteed Highest

|- CPU #0 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #1 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #2 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.56 ( 37)

|- CPU #3 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #4 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #5 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.56 ( 37)

|- CPU #6 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #7 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.56 ( 37)

|- CPU #8 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #9 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.56 ( 37)

|- CPU #10 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.56 ( 37)

|- CPU #11 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #12 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #13 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.56 ( 37)

|- CPU #14 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #15 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #16 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #17 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #18 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #19 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #20 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #21 399.95 ( 4) 1999.75 ( 20) 1999.75 ( 20) 3699.55 ( 37)

|- CPU #22 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #23 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #24 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #25 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #26 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #27 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #28 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #29 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #30 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #31 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #32 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #33 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #34 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #35 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #36 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #37 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #38 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #39 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #40 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #41 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #42 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #43 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.56 ( 37)

|- CPU #44 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #45 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #46 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #47 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #48 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.56 ( 37)

|- CPU #49 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #50 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.56 ( 37)

|- CPU #51 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #52 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #53 399.95 ( 4) 1999.75 ( 20) 1999.75 ( 20) 3699.54 ( 37)

|- CPU #54 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #55 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #56 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.56 ( 37)

|- CPU #57 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #58 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #59 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #60 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #61 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #62 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #63 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #64 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #65 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #66 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.56 ( 37)

|- CPU #67 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #68 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #69 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #70 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.56 ( 37)

|- CPU #71 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.56 ( 37)

|- CPU #72 399.95 ( 4) 1999.75 ( 20) 1999.75 ( 20) 3699.53 ( 37)

|- CPU #73 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #74 399.95 ( 4) 1999.75 ( 20) 1999.75 ( 20) 3699.54 ( 37)

|- CPU #75 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #76 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.56 ( 37)

|- CPU #77 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #78 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #79 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.56 ( 37)

|- CPU #80 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #81 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #82 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #83 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #84 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #85 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #86 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #87 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.56 ( 37)

|- CPU #88 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #89 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #90 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #91 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #92 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #93 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #94 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #95 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #96 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.56 ( 37)

|- CPU #97 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #98 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #99 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #100 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #101 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #102 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #103 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #104 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.56 ( 37)

|- CPU #105 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #106 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #107 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #108 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #109 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #110 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #111 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #112 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.56 ( 37)

|- CPU #113 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #114 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #115 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #116 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #117 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #118 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #119 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #120 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #121 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #122 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #123 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #124 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #125 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #126 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

|- CPU #127 399.95 ( 4) 1999.76 ( 20) 1999.76 ( 20) 3699.55 ( 37)

Power, Current & Thermal

|- Temperature Offset:Junction TjMax [ 49: 12 C]

|- CPPC Energy Preference EPP [Missing]

|- Digital Thermal Sensor DTS [Capable]

|- Power Limit Notification PLN [Missing]

|- Package Thermal Management PTM [Missing]

|- Thermal Monitor 1 TTP [ Enable]

|- Thermal Monitor 2 HTC [ Enable]

|- Thermal Design Power TDP [ 480 W]

|- Minimum Power Min [ 104 W]

|- Maximum Power Max [ 378 W]

|- Thermal Design Power Package [Disable]

|- Power Limit PL1 [ 0 W]

|- Time Window TW1 [ 0 ns]

|- Power Limit PL2 [ 0 W]

|- Time Window TW2 [ 0 ns]

|- Thermal Design Power Core [Disable]

|- Power Limit PL1 [ 0 W]

|- Time Window TW1 [ 0 ns]

|- Thermal Design Power Uncore [Disable]

|- Power Limit PL1 [ 0 W]

|- Time Window TW1 [ 0 ns]

|- Thermal Design Power DRAM [Disable]

|- Power Limit PL1 [ 0 W]

|- Time Window TW1 [ 0 ns]

|- Thermal Design Power Platform [Disable]

|- Power Limit PL1 [ 0 W]

|- Time Window TW1 [ 0 ns]

|- Power Limit PL2 [ 0 W]

|- Time Window TW2 [ 0 ns]

|- Package Power Tracking PPT [ 4 W]

|- Electrical Design Current EDC [ 444 A]

|- Thermal Design Current TDC [ 111 A]

|- Core Thermal Point

|- Package Thermal Point

|- Thermal Monitor Trip Limit [ 115 C]

|- HTC Temperature Limit Limit [ 106 C]

|- HTC Temperature Hysteresis Threshold [ 2 C]

|- Units

|- Power watt [ 0.125000000]

|- Energy joule [ 0.000015259]

|- Window second [ 0.000976562]

CPU Pkg Apic Core/Thread Caches (w)rite-Back (i)nclusive

# ID ID CCD CCX ID/ID L1-Inst Way L1-Data Way L2 Way L3 Way

000:BSP 0 0 0 0 0 32 8 32 8 512 8 i 262144 16w

001: 0 2 0 0 1 0 32 8 32 8 512 8 i 262144 16w

002: 0 4 0 0 2 0 32 8 32 8 512 8 i 262144 16w

003: 0 6 0 0 3 0 32 8 32 8 512 8 i 262144 16w

004: 0 8 0 1 4 0 32 8 32 8 512 8 i 262144 16w

005: 0 10 0 1 5 0 32 8 32 8 512 8 i 262144 16w

006: 0 12 0 1 6 0 32 8 32 8 512 8 i 262144 16w

007: 0 14 0 1 7 0 32 8 32 8 512 8 i 262144 16w

008: 0 16 2 2 8 0 32 8 32 8 512 8 i 262144 16w

009: 0 18 2 2 9 0 32 8 32 8 512 8 i 262144 16w

010: 0 20 2 2 10 0 32 8 32 8 512 8 i 262144 16w

011: 0 22 2 2 11 0 32 8 32 8 512 8 i 262144 16w

012: 0 24 2 3 12 0 32 8 32 8 512 8 i 262144 16w

013: 0 26 2 3 13 0 32 8 32 8 512 8 i 262144 16w

014: 0 28 2 3 14 0 32 8 32 8 512 8 i 262144 16w

015: 0 30 2 3 15 0 32 8 32 8 512 8 i 262144 16w

016: 0 32 4 4 16 0 32 8 32 8 512 8 i 262144 16w

017: 0 34 4 4 17 0 32 8 32 8 512 8 i 262144 16w

018: 0 36 4 4 18 0 32 8 32 8 512 8 i 262144 16w

019: 0 38 4 4 19 0 32 8 32 8 512 8 i 262144 16w

020: 0 40 4 5 20 0 32 8 32 8 512 8 i 262144 16w

021: 0 42 4 5 21 0 32 8 32 8 512 8 i 262144 16w

022: 0 44 4 5 22 0 32 8 32 8 512 8 i 262144 16w

023: 0 46 4 5 23 0 32 8 32 8 512 8 i 262144 16w

024: 0 48 6 6 24 0 32 8 32 8 512 8 i 262144 16w

025: 0 50 6 6 25 0 32 8 32 8 512 8 i 262144 16w

026: 0 52 6 6 26 0 32 8 32 8 512 8 i 262144 16w

027: 0 54 6 6 27 0 32 8 32 8 512 8 i 262144 16w

028: 0 56 6 7 28 0 32 8 32 8 512 8 i 262144 16w

029: 0 58 6 7 29 0 32 8 32 8 512 8 i 262144 16w

030: 0 60 6 7 30 0 32 8 32 8 512 8 i 262144 16w

031: 0 62 6 7 31 0 32 8 32 8 512 8 i 262144 16w

032: 0 64 4 8 32 0 32 8 32 8 512 8 i 262144 16w

033: 0 66 4 8 33 0 32 8 32 8 512 8 i 262144 16w

034: 0 68 4 8 34 0 32 8 32 8 512 8 i 262144 16w

035: 0 70 4 8 35 0 32 8 32 8 512 8 i 262144 16w

036: 0 72 4 9 36 0 32 8 32 8 512 8 i 262144 16w

037: 0 74 4 9 37 0 32 8 32 8 512 8 i 262144 16w

038: 0 76 4 9 38 0 32 8 32 8 512 8 i 262144 16w

039: 0 78 4 9 39 0 32 8 32 8 512 8 i 262144 16w

040: 0 80 5 10 40 0 32 8 32 8 512 8 i 262144 16w

041: 0 82 5 10 41 0 32 8 32 8 512 8 i 262144 16w

042: 0 84 5 10 42 0 32 8 32 8 512 8 i 262144 16w

043: 0 86 5 10 43 0 32 8 32 8 512 8 i 262144 16w

044: 0 88 5 11 44 0 32 8 32 8 512 8 i 262144 16w

045: 0 90 5 11 45 0 32 8 32 8 512 8 i 262144 16w

046: 0 92 5 11 46 0 32 8 32 8 512 8 i 262144 16w

047: 0 94 5 11 47 0 32 8 32 8 512 8 i 262144 16w

048: 0 96 6 12 48 0 32 8 32 8 512 8 i 262144 16w

049: 0 98 6 12 49 0 32 8 32 8 512 8 i 262144 16w

050: 0 100 6 12 50 0 32 8 32 8 512 8 i 262144 16w

051: 0 102 6 12 51 0 32 8 32 8 512 8 i 262144 16w

052: 0 104 6 13 52 0 32 8 32 8 512 8 i 262144 16w

053: 0 106 6 13 53 0 32 8 32 8 512 8 i 262144 16w

054: 0 108 6 13 54 0 32 8 32 8 512 8 i 262144 16w

055: 0 110 6 13 55 0 32 8 32 8 512 8 i 262144 16w

056: 0 112 7 14 56 0 32 8 32 8 512 8 i 262144 16w

057: 0 114 7 14 57 0 32 8 32 8 512 8 i 262144 16w

058: 0 116 7 14 58 0 32 8 32 8 512 8 i 262144 16w

059: 0 118 7 14 59 0 32 8 32 8 512 8 i 262144 16w

060: 0 120 7 15 60 0 32 8 32 8 512 8 i 262144 16w

061: 0 122 7 15 61 0 32 8 32 8 512 8 i 262144 16w

062: 0 124 7 15 62 0 32 8 32 8 512 8 i 262144 16w

063: 0 126 7 15 63 0 32 8 32 8 512 8 i 262144 16w

064: 0 1 0 0 0 1 32 8 32 8 512 8 i 262144 16w

065: 0 3 0 0 1 1 32 8 32 8 512 8 i 262144 16w

066: 0 5 0 0 2 1 32 8 32 8 512 8 i 262144 16w

067: 0 7 0 0 3 1 32 8 32 8 512 8 i 262144 16w

068: 0 9 0 1 4 1 32 8 32 8 512 8 i 262144 16w

069: 0 11 0 1 5 1 32 8 32 8 512 8 i 262144 16w

070: 0 13 0 1 6 1 32 8 32 8 512 8 i 262144 16w

071: 0 15 0 1 7 1 32 8 32 8 512 8 i 262144 16w

072: 0 17 2 2 8 1 32 8 32 8 512 8 i 262144 16w

073: 0 19 2 2 9 1 32 8 32 8 512 8 i 262144 16w

074: 0 21 2 2 10 1 32 8 32 8 512 8 i 262144 16w

075: 0 23 2 2 11 1 32 8 32 8 512 8 i 262144 16w

076: 0 25 2 3 12 1 32 8 32 8 512 8 i 262144 16w

077: 0 27 2 3 13 1 32 8 32 8 512 8 i 262144 16w

078: 0 29 2 3 14 1 32 8 32 8 512 8 i 262144 16w

079: 0 31 2 3 15 1 32 8 32 8 512 8 i 262144 16w

080: 0 33 4 4 16 1 32 8 32 8 512 8 i 262144 16w

081: 0 35 4 4 17 1 32 8 32 8 512 8 i 262144 16w

082: 0 37 4 4 18 1 32 8 32 8 512 8 i 262144 16w

083: 0 39 4 4 19 1 32 8 32 8 512 8 i 262144 16w

084: 0 41 4 5 20 1 32 8 32 8 512 8 i 262144 16w

085: 0 43 4 5 21 1 32 8 32 8 512 8 i 262144 16w

086: 0 45 4 5 22 1 32 8 32 8 512 8 i 262144 16w

087: 0 47 4 5 23 1 32 8 32 8 512 8 i 262144 16w

088: 0 49 6 6 24 1 32 8 32 8 512 8 i 262144 16w

089: 0 51 6 6 25 1 32 8 32 8 512 8 i 262144 16w

090: 0 53 6 6 26 1 32 8 32 8 512 8 i 262144 16w

091: 0 55 6 6 27 1 32 8 32 8 512 8 i 262144 16w

092: 0 57 6 7 28 1 32 8 32 8 512 8 i 262144 16w

093: 0 59 6 7 29 1 32 8 32 8 512 8 i 262144 16w

094: 0 61 6 7 30 1 32 8 32 8 512 8 i 262144 16w

095: 0 63 6 7 31 1 32 8 32 8 512 8 i 262144 16w

096: 0 65 4 8 32 1 32 8 32 8 512 8 i 262144 16w

097: 0 67 4 8 33 1 32 8 32 8 512 8 i 262144 16w

098: 0 69 4 8 34 1 32 8 32 8 512 8 i 262144 16w

099: 0 71 4 8 35 1 32 8 32 8 512 8 i 262144 16w

100: 0 73 4 9 36 1 32 8 32 8 512 8 i 262144 16w

101: 0 75 4 9 37 1 32 8 32 8 512 8 i 262144 16w

102: 0 77 4 9 38 1 32 8 32 8 512 8 i 262144 16w

103: 0 79 4 9 39 1 32 8 32 8 512 8 i 262144 16w

104: 0 81 5 10 40 1 32 8 32 8 512 8 i 262144 16w

105: 0 83 5 10 41 1 32 8 32 8 512 8 i 262144 16w

106: 0 85 5 10 42 1 32 8 32 8 512 8 i 262144 16w

107: 0 87 5 10 43 1 32 8 32 8 512 8 i 262144 16w

108: 0 89 5 11 44 1 32 8 32 8 512 8 i 262144 16w

109: 0 91 5 11 45 1 32 8 32 8 512 8 i 262144 16w

110: 0 93 5 11 46 1 32 8 32 8 512 8 i 262144 16w

111: 0 95 5 11 47 1 32 8 32 8 512 8 i 262144 16w

112: 0 97 6 12 48 1 32 8 32 8 512 8 i 262144 16w

113: 0 99 6 12 49 1 32 8 32 8 512 8 i 262144 16w

114: 0 101 6 12 50 1 32 8 32 8 512 8 i 262144 16w

115: 0 103 6 12 51 1 32 8 32 8 512 8 i 262144 16w

116: 0 105 6 13 52 1 32 8 32 8 512 8 i 262144 16w

117: 0 107 6 13 53 1 32 8 32 8 512 8 i 262144 16w

118: 0 109 6 13 54 1 32 8 32 8 512 8 i 262144 16w

119: 0 111 6 13 55 1 32 8 32 8 512 8 i 262144 16w

120: 0 113 7 14 56 1 32 8 32 8 512 8 i 262144 16w

121: 0 115 7 14 57 1 32 8 32 8 512 8 i 262144 16w

122: 0 117 7 14 58 1 32 8 32 8 512 8 i 262144 16w

123: 0 119 7 14 59 1 32 8 32 8 512 8 i 262144 16w

124: 0 121 7 15 60 1 32 8 32 8 512 8 i 262144 16w

125: 0 123 7 15 61 1 32 8 32 8 512 8 i 262144 16w

126: 0 125 7 15 62 1 32 8 32 8 512 8 i 262144 16w

127: 0 127 7 15 63 1 32 8 32 8 512 8 i 262144 16w

Sign up for free

to join this conversation on GitHub.

Already have an account?

Sign in to comment