Created

February 14, 2022 16:23

-

-

Save cyring/6ed0f017ed196fd385934866ce47ce40 to your computer and use it in GitHub Desktop.

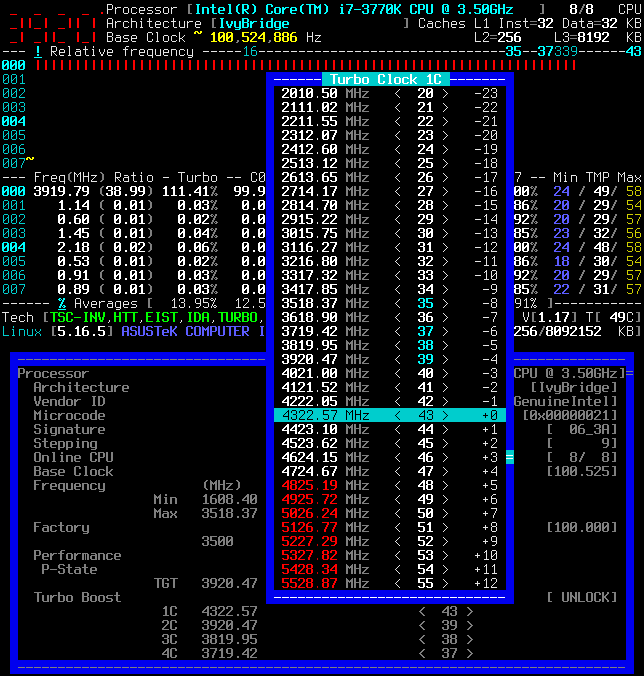

Intel Core i7-3770K

This file contains bidirectional Unicode text that may be interpreted or compiled differently than what appears below. To review, open the file in an editor that reveals hidden Unicode characters.

Learn more about bidirectional Unicode characters

| CoreFreq version 1.90 |

Sign up for free

to join this conversation on GitHub.

Already have an account?

Sign in to comment

Processor

Idle

Package C-states

Single Core stressed

All Cores stressed

System Information

Topology

Dashboard

Sensors

Idle

Stressed

Turbo - Random CPU

Kernel

Drivers

Tasks

BIOS

Slice counters

Tools - Conic - Hyperboloid of two sheets