Blog 2020/9/30

<- previous | index | next ->

Let's simulate a zener diode voltage regulator using LTspice.

Our circuit is a 12V AC "wall wart", into a bridge rectifier, a smoothing capacitor, a zener-resistor pair which forms the voltage regulator, and a resistive load.

LTspice models used:

- 1N4001 1 Amp recitifying diode, from http://ltwiki.org/index.php?title=Standard.dio

- 1N754 500mW 6.8V Zener diode, from http://ltwiki.org/index.php?title=Standard.dio

To use the custom models, click the .op button and paste in the model definitions, then control + right-click each component and enter the custom model in the "Value" field:

Here, you can see regulator working:

The peak-to-peak voltage of the unregulated rectified wave form is just shy of 1 Volt:

Zooming in on the regulated wave form, we see the peak-to-peak is about 41 millivolts:

41V over 924mV is about 4.4%, which converts to about about 27dB of regulation.

The datasheet uses 20mA as the test current, and lists the maximum allowed current as 55mA:

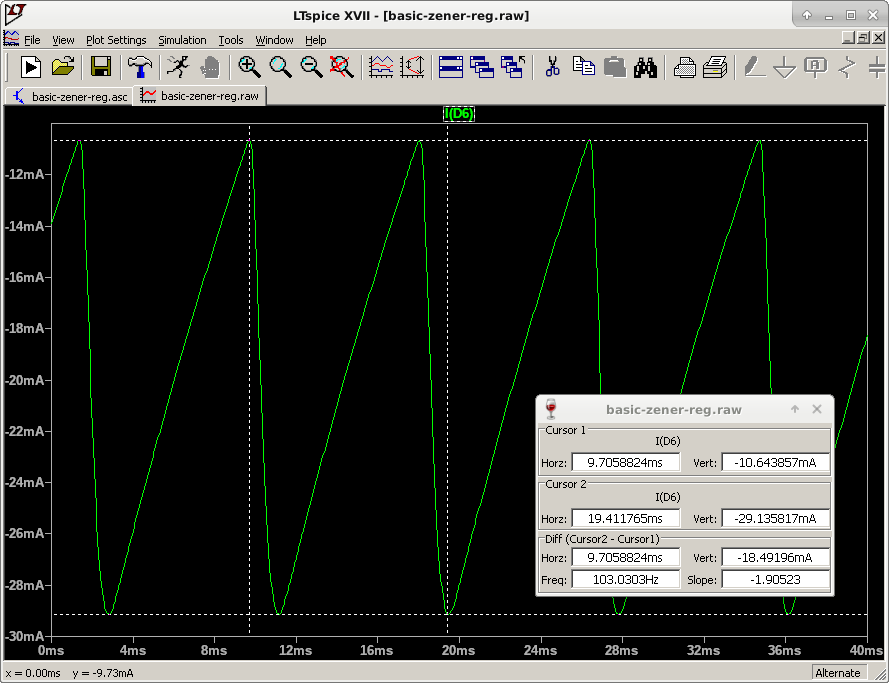

In our circuit, the zener current varies between about 10 and 30mA, so we are averaging near 20 and are below 55mA:

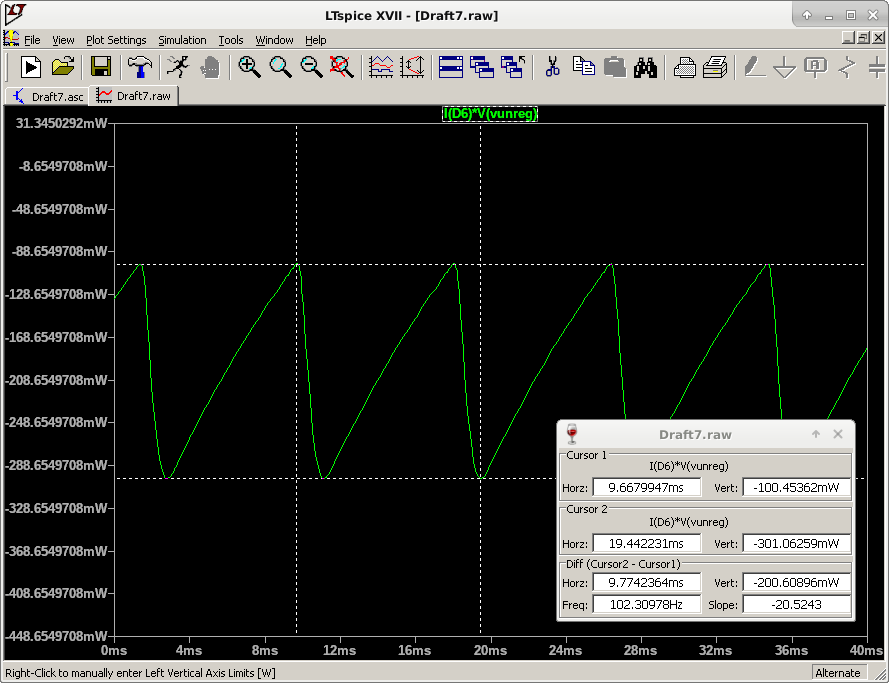

The 1N754 is a 500mW part, let's check the power dissipation. Select the plot window, then from the "Plot Settings" menu, select "Add trace". Type in I(D6)*V(vunreg) into the expression box:

The power varies between 100 and 300mW, and it looks like the duty cycle is 50%, so the average power dissipation is 200mW, which is ok:

Now let's push it out of regulation by increasing the current drawn by the load resistor:

- Click the

.opbutton and add a spice directive to step a parameter calledRLOADthrough a list of values:.step param RLOAD list 150 120 100 82 - Right-click the Rload resistor and change its value to

{RLOAD}(note the curly braces)

Now we can see the zener progressively fall out of regulation by looking at Vz. As the load resistance gets lower, the load resistor draws more current, which pushed the zener out of regulation. The blue trace shows partial regulation, while the green trace is completely unregulated.

We can also see this by looking at the current through the zener. Here, each progressively lower value of load resistance pushes the zener current closer to 0mA. The blue trace shows the zener current "clipping" at 0mA, falling in and out of regulation. The green trace is flat-lined at 0mA, indicating the zener has completely fallen out of regulation.