Blog 2020/10/2

<- previous | index | next ->

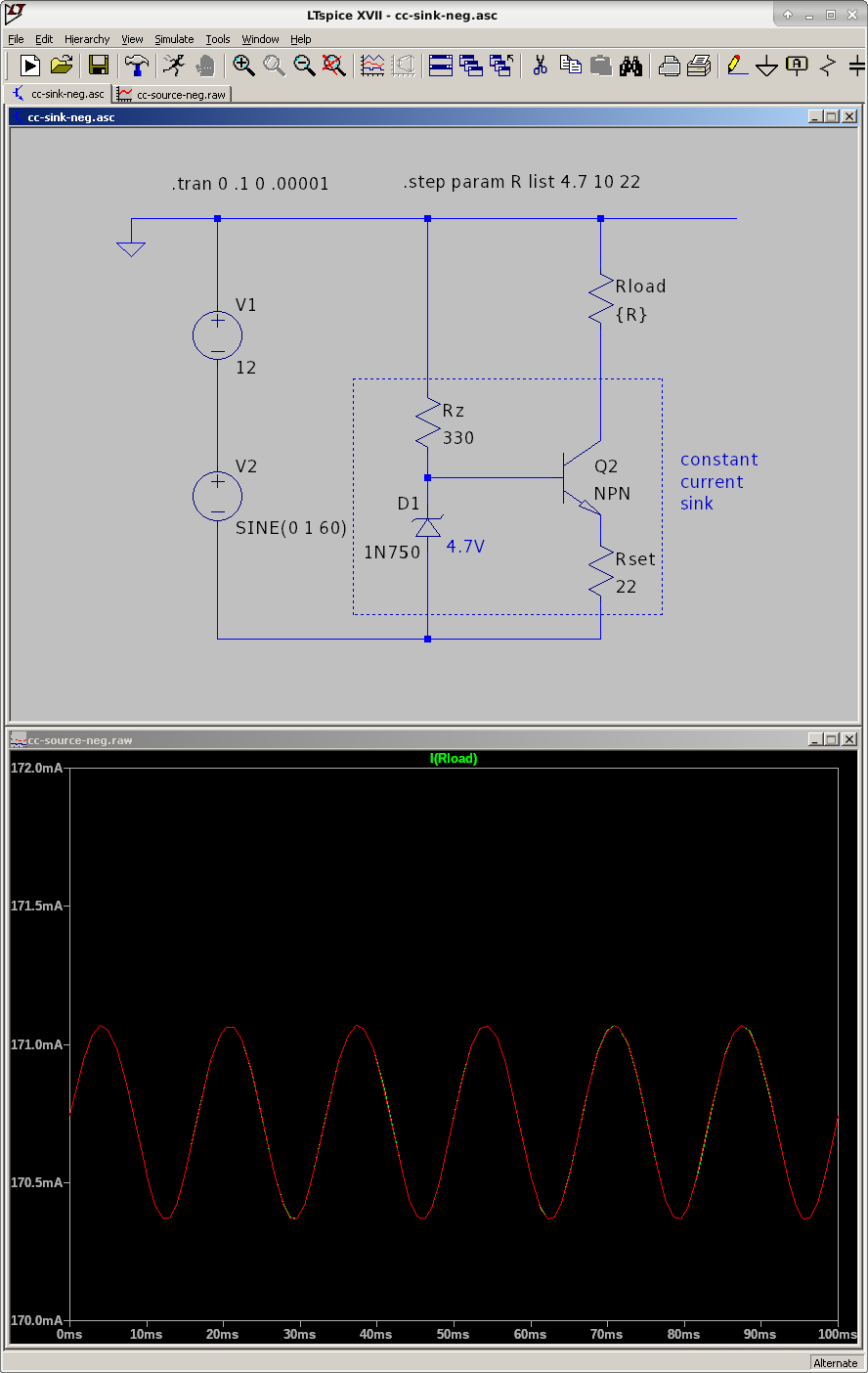

A basic constant-current source or sink can be constructed from a Zener, a BJT, and a few resistors.

Because it is easy to forget the particular arrangement of the parts for each of the four configurations, I've enumerated each of them below.

In each LTspice simulation, the voltage source is 12V +/- 1V @ 60Hz, which approximates a rectified and filtered but unregulated voltage rail.

Each screenshot actually shows three simulations, where Rload is 4.7, 10 and 22 Ohms. This is difficult to see because the graphs are right on top of each other (indicating that the current regulation is independent of the load resistor value).

The current regulation performance isn't spectacular, because the Zener's voltage regulation isn't perfect. These circuits are useful as a conceptual base to start from, but could be improved upon, perhaps with cascaded Zener shunt regulators, or by replacing Rz with a JFET.